#### ABSTRACT

LAMMERT, ADAM CRAWFORD. Searching for Better Logic Circuits: Using Artificial Intelligence Techniques to Automate Digital Design. (Under the direction of Dr. Edward Willmore Davis Jr.)

Logic circuits are at the core of modern computing. The process of designing circuits which are efficient is thus of critical importance. Usually, logic circuits are designed by human beings who have a specific repertoire of conventional design techniques. These techniques limit the solutions that may be considered during the design process in both form and quality. The limits guide designers through the immense realm of possible circuits, thus making the problem more manageable. Simultaneously, the limits sometimes eliminate from consideration circuits which are optimal in terms of size, depth, etc. By exploring the full range of possible solutions, circuits could be discovered which are superior to the best known human designs. Automated design techniques borrowed from artificial intelligence have allowed exactly that. Specifically, the application of genetic algorithms has allowed the creation of circuits which are substantially superior to the best known human designs. This paper expands on such previous research with a three-fold approach. This approach is comprised of (1) two distinct optimizations for the application of genetic algorithms to design, (2) the formulation and implementation of a systematic search technique to the problem and (3) a comparison of the relative merits of the optimized genetic algorithm and the systematic search technique. It is contended that both genetic algorithms and systematic search can be preferable depending on the situation at hand.

# SEARCHING FOR BETTER LOGIC CIRCUITS: USING ARTIFICIAL INTELLIGENCE TECHNIQUES TO AUTOMATE DIGITAL DESIGN

# by ADAM CRAWFORD LAMMERT

A thesis submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Master of Science

# **COMPUTER SCIENCE**

Raleigh, NC

2006

**APPROVED BY:**

Chair of Advisory Committee

#### BIOGRAPHY

Adam Crawford Lammert was born in Pittsburgh, Pennsylvania and raised in Western New York, near Buffalo. His interest in science developed early on, and has always been highly varied. As an undergraduate at Vassar College, his interest was captured by the interplay of mind and machine. As a result, he studied both Cognitive Science and Computer Science. His research at Vassar focused on robotic implementations of intelligence. After graduating, he moved south to attend North Carolina State University. There, he studied primarily Computer Science. The research at NCSU surrounded Artificial Intelligence, and its application to circuit design. That research culminated in this thesis. Currently, Adam is living in the San Francisco Bay Area and working as a laboratory assistant in the field of auditory perception.

### ACKNOWLEDGEMENTS

I would like to acknowledge and offer my sincerest appreciation to Dr. Edward Davis for his intellectual and editorial support throughout this process, as well as his consistent encouragement. Also, to Catharina Berglund for being my most important moral and emotional support throughout this process. Dr. Dennis Bahler and Dr. James Lester helped guide and enlighten me during discussions in and out of the classroom. To Dr. David Thuente, as well, for his genuine kindness.

# TABLE OF CONTENTS

| List of Figures.                                     | vi |

|------------------------------------------------------|----|

| 1 Introduction.                                      | 1  |

| 1.1 Essential Concepts.                              | 5  |

| 1.2 Forthcoming Topics and Sections.                 | 6  |

| 2 Logic Circuit Design.                              | 7  |

| 2.1 Boolean Logic.                                   | 8  |

| 2.2 Logical Forms and Simplification Techniques      | 14 |

| 2.3 Logic Circuits.                                  | 17 |

| 3 Search Techniques from Artificial Intelligence.    | 19 |

| 3.1 Search Basics.                                   | 19 |

| 3.2 Systematic Search.                               |    |

| 3.3 Local Search.                                    |    |

| 4 Applying Search Techniques to Logic Circuit Design |    |

| 4.1 Genetic Algorithms for Logic Circuit Design      |    |

| 4.2 Two GA Camps                                     |    |

| 4.3 Intrinsic Evolution.                             | 34 |

| 4.4 Extrinsic Evolution.                             |    |

| 4.5 Systematic Search for Logic Circuit Design       |    |

| 5 Optimization of Genetic Algorithms.                | 41 |

| 5.1 Optimizing the Circuit-Size Evaluator.           | 43 |

| 5.2 Evidence for the New Size Evaluator              | 46 |

| 5.3        | Optimizing the Functionality Evaluator.       | 48  |

|------------|-----------------------------------------------|-----|

| 5.4        | Evidence for the New Functionality Evaluator. | 50  |

| 5.5        | Combining the New Optimizations.              | 52  |

| 6 Develop  | ing Systematic Search.                        | .53 |

| 6.1        | Skepticism About Systematic Search.           | 54  |

| 6.2        | Re-Formulating Logic Circuit Design.          | 55  |

| 6.3        | Implementing Systematic Search.               | .59 |

| 7 Compar   | ison of Relevant Search Techniques.           | 62  |

| 7.1        | Solution Quality.                             | 63  |

| 7.2        | Time Requirements, Considered Empirically.    | 64  |

| 7.3        | Space Requirements.                           | 67  |

| 7.4        | Trade-Off Conclusions.                        | 68  |

| 8 Conclus  | ions and Future Work.                         | 68  |

| 8.1        | Conclusions.                                  | .69 |

| 8.2        | Future Work.                                  | 71  |

| References | 3                                             | 73  |

| Appendice  | S                                             | 78  |

| Ap         | pendix A                                      | 79  |

| Ap         | pendix B.                                     | 89  |

# LIST OF FIGURES

| Figure 1: Table of 2-Input Boolean Operators.              | 9  |

|------------------------------------------------------------|----|

| Figure 2: Truth Table for $F = X^*Y + X^*Z$ .              | 11 |

| Figure 3: Logical Operators and Corresponding Schematics.  | 17 |

| Figure 4: The Crossover Operator for Genetic Algorithms.   |    |

| Figure 5: The Array Formulation of Logic Circuits.         |    |

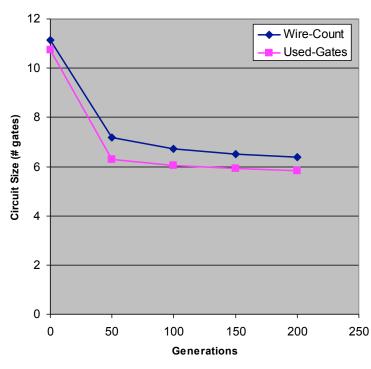

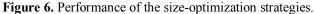

| Figure 6: Performance Data from Size-Optimization Schemes  | 46 |

| Figure 7: Normalized Data from Size-Optimization Schemes.  | 47 |

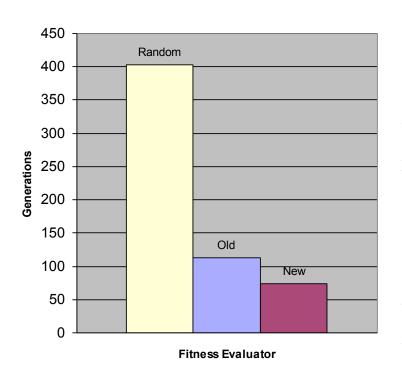

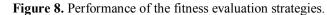

| Figure 8: Performance Data from Fitness Evaluators.        |    |

| Figure 9: Normalized Data from Fitness Evaluators.         | 51 |

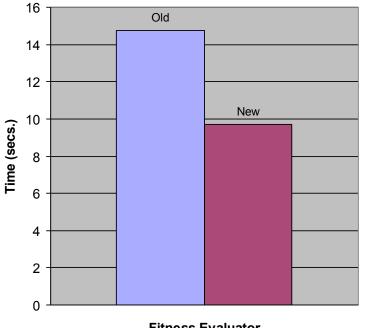

| Figure 10: Normalized Data from Combined Optimizations.    | 52 |

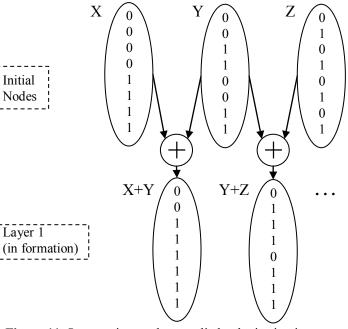

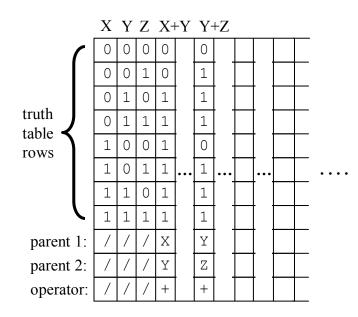

| Figure 11: The Systematic Search Formulation.              | 55 |

| Figure 12: The Systematic Search Implementation.           | 59 |

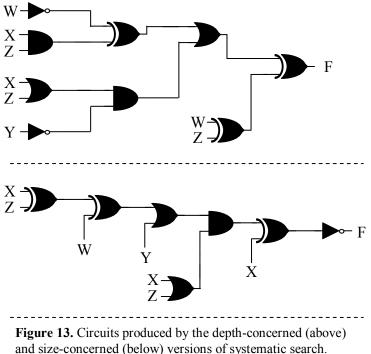

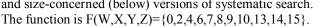

| Figure 13: Circuits Produced by Systematic Search, Set One | 60 |

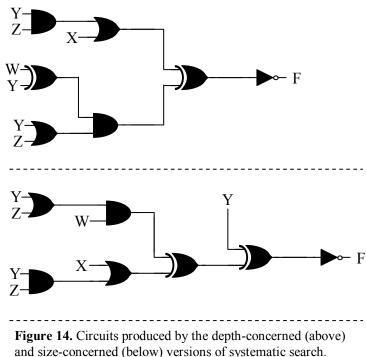

| Figure 14: Circuits Produced by Systematic Search, Set Two | 61 |

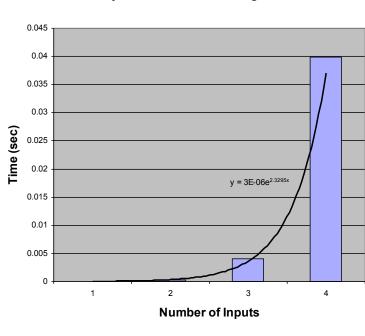

| Figure 15: Scaling Performance of the Genetic Algorithm.   | 65 |

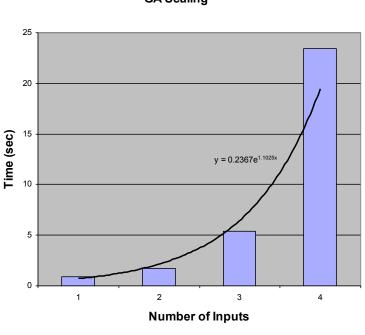

| Figure 16: Scaling Performance of Systematic Search.       | 66 |

## **1** Introduction

Central to modern computing is the ability to perform logic. Indeed, logic is the framework on which the very concept of modern computation is built. In essence, computation is a careful orchestration of logical operations and functions. This logic can be simple or complex, but logic is always present at the heart of whatever computation is taking place. Computing hardware serves the purpose of facilitating this logic in a physical device. In the hardware, logical operations physically take place.

In its most fundamental form, the logic in computers is facilitated by digital logic circuits. Moreover, the basic components of these circuits are known as logic gates. Gates carry out only a single logical operation such as logical AND, OR, or NOT. It is true that these gates can constitute logic circuits all on their own. However, they are most often combined and interconnected in various ways to create more complex circuits. Now, provided that the appropriate gates and connections are chosen, it is possible to create a circuit which implements any logical function. The act of using gates and connections to build up circuits in this way is a process of careful design. Designing circuits is, naturally, an immensely important process. Without careful and correct design of digital logic, computers would not be able to function. Aside from being important, though, there is an ironic aspect of digital design. Specifically, design is both simple and difficult, simultaneously. This dichotomy is important to understand, before advancing the discussion any further.

The dichotomy inherent in designing digital logic circuits—that it is both simple and difficult—is by no means limited to the realm of computers. Rather, it is characteristic of a very important class of systems. Namely, digital design is one example of a discrete

combinatorial system [sensu 24,25]. The characteristics of such a system are that it has a finite collection of discrete elements which are combined to create new distinct objects. These newly created objects have different properties than the basic elements themselves. In the case of logic circuit design, gates are the discrete elements, and they are combined to create new circuits which function differently than any of the individual gates. In addition, there is no limit on the size of the combination. This is true of any discrete combinatorial system. In this case, it means that circuits may be composed of an arbitrarily large number of gates. This last fact means that there are an infinite number of new objects that can be created with a system like this. Therein lies the root of the dichotomy in digital design. First, designing new circuits is basically simple because it involves a finite number of elements that are combined in straight-forward ways. However, because combinations can be arbitrarily large, the difficult part is getting the circuit you need. More specifically, the difficulty lies in finding which of the infinite number of possible circuits is the one you want. Anyone can throw together a few gates to create a new circuit, but designing one that operates in just the right way can take considerable time and effort.

It is worth noting that discrete combinatorial systems are amongst the most interesting and useful in the world. For instance, all natural human languages are of this type. Words are combined in infinite variety to make sentences, which have a meaning all their own. Moreover, the genetic code contained in our DNA is another discrete combinatorial system. Obviously, there is much power to behold in a system of this kind. However, most of the systems we encounter in our world are not of this type. Rather, we most often come across blended systems [24,25], such as that of color. In systems like color, components are also put together to yield a new result. However, the resulting combinations have properties which are not fully distinct from the properties of the components. Rather, the properties of the result are, in some sense, an average of the components. For instance, when two primary colors are combined, the characteristics of the new color are a mixture of the initial two. Thus, the properties that are possible to observe in a blended system are entirely limited by the properties of the component parts. This is true of most systems we encounter day-to-day, such as sound, meteorology and even cooking [24,25].

The fact that logic circuit design is a discrete combinatorial system means that the rules of design are simple, but that achieving design goals can be difficult. Fortunately, the simple rules of design are powerful enough to allow the creation of any circuit we want. However, it is the responsibility of the designer to find the circuit which best suits the design problem at hand. Conventionally, the designer of digital logic circuits is a human being. These people who are responsible for designing circuits must, obviously, have extensive knowledge of formal logic and of circuit operation. In most cases, these designers also know several established design methods which they were taught to make the process easier for people to manage. For expert designers, they may have personalized these established methods using experience and human creativity, or they may have created their own methods for design. However, the fact that creativity often enters into the design process (when humans are designing) doesn't mean that creativity is a prerequisite for the ability to design circuits of this type. Indeed, in recent years, the idea of automating the design process has spawned an interesting and fruitful field of research in computer science. In this research, circuit design is treated like any other computational problem. By automating design, the goal is to remove human effort, and human limitations, from the design process. This can be

done by taking advantage of what computers do very well, quickly examine a huge number of possible solutions.

Automation of digital design is desirable because it removes the need for human effort in deriving new circuits. However, there are other reasons which are equally compelling. One such reason, which may not be immediately obvious, is the pursuit of superior designs. As we will see, the established design methods allow human beings to arrive at circuit designs quickly and accurately. This speed and accuracy, however, is gained by limiting the realm of possible solutions. In using these methods, one is forced to substantially limit the available components, the ways those components can be configured, or some such property of the design problem. By enforcing these limitations, it is ensured that the design problem will be tractable for human beings. However, it is also highly possible that the results will be of limited optimality. As previously mentioned, some designers are experienced enough, or clever enough, to go beyond the strong limitations of the established methods. However, some number of strong limitations are always in place. In many cases, this keeps human designers from creating solutions which are optimal. By automating the design process, it is possible to take advantage of the speed with which computers can consider possible solutions. Thus, it is possible to substantially loosen the limitations, consider a wider array of possibilities, and to consequently arrive at a superior solution. Moreover, it is possible to do all this in a similar, if not better, amount of time.

#### 1.1 Essential Concepts

Before proceeding, it is necessary to explain what is meant by 'optimal', in terms of circuit design. More generally, we need to define what makes one design solution better than another. Truth be told, there is no universal sense of what makes one circuit better than another. Rather, it all depends on what criteria are selected as important. However, in this paper, there is a small selection of criteria that we will be dealing with. First and foremost, is the criterion of functionality, which is of paramount importance. A circuit which always produces the correct outputs is obviously superior to one which does not. However, functionality is not always a binary property (i.e. it works perfectly, or doesn't work at all). There are levels of functionality which can be examined, and this will become important later, for some of the new research presented in this paper. Another important circuit property that we will focus on is size. In this paper, what is meant by size is the number of gates used to construct the circuit. Obviously, smaller sizes make a circuit more efficient and this is highly desirable. Depth of a circuit will also be considered, by which is meant the longest chain of gates needed to get from the inputs of a circuit to the outputs. Other criteria, including power utilization, will be mentioned and explained in the paper, but are of lesser importance.

It is also important to note that when we are talking about computers designing circuits, we are talking specifically about designing structural representations for the circuits. That is, a representation which defines the circuit in terms of components and connections. The design specification must go beyond a simple black-box description of the circuit's behavior, but does not need to go so far as to explain the physical properties of the circuit.

The functionality of the circuit must be derivable from the representation, in order to evaluate it. Moreover, the types of components used, and the connections between them must be included in the representation. However, exact spatial dimensions and details of operation are extraneous to the discussion presented here.

## 1.2 Forthcoming Topics and Sections

In automatically designing logic circuits of this type, techniques from artificial intelligence have been extremely useful. Researchers who broke ground in this area saw that logic circuit design could be formulated as a puzzle, and puzzle-solving is an area of great success within artificial intelligence. Specifically, genetic algorithms have been highly researched as a candidate for automating circuit design. Moreover, there has been a good amount of success with using these algorithms. Genetic algorithms have been able to produce better results than human designers, and in a shorter period of time. In that vain, the first half of the original research described in this paper will focus on genetic algorithms. Attempts are made to improve the performance of genetic algorithms for this purpose. Improvements are shown in both the time required to arrive at results and the quality of those results.

The second half of the research in this paper involves the application of an artificial intelligence technique that has, to our knowledge, never before been used for this purpose. Specifically, an exhaustive search algorithm is employed. The results of this research show that there are advantages and disadvantages to this approach with respect to genetic algorithms. There is a clear trade-off between the two approaches. At the same time, the

research contained herein highlights the inherent difficulty of this type of design, regardless of the approach. Nevertheless, automated logic circuit design is possible, and its results are promising.

Section 2 of this paper contains an overview of basic knowledge in logic circuit design and Section 3 contains an overview of relevant artificial intelligence techniques. In Section 4, one can find a review of concepts and relevant literature involving the application of artificial intelligence techniques to automated circuit design. Section 5 begins a discussion of new research, where a successful attempt is made to optimize genetic algorithms for automation. The discussion of new research continues in Section 6, where automated circuit design is performed by an artificial intelligence technique (exhaustive search) that is previously unutilized for this purpose. Section 7 compares the genetic algorithm approach to exhaustive search. Finally, Section 8 contains some final discussion points and suggestions for future work in this area.

## 2 Logic Circuit Design

For the realm of computer science, the important principles of logic were first laid out in 1854 by George Boole. His work, entitled *An Investigation of the Laws of Thought* [2], presented a two-valued algebra which constituted a formal and systematic treatment of logic [6]. Since then, this system of logic has commonly become known as Boolean algebra, in honor of his seminal efforts [12]. Boolean algebra is the fundamental framework for all logic in modern computers. As such, the ideas of this logic should be familiar to computer scientists. Nonetheless, it serves us well to briefly review the essential ideas, but with an eye towards understanding logical circuit design.

#### 2.1 Boolean Logic

In essence, Boolean algebra contains two types of important objects, variables and operators. From these two basic items, complex logical expressions can be built. The variables, like variables in any other mathematical system, have names associated with them (i.e. X, Y, Z, etc.). They can also take on one of two values, namely 0 and 1. In the usual interpretation, a value of 0 corresponds to a logical 'false' and a value of 1 corresponds to logical 'true'. Although it is possible to conceive of Boolean algebra with more than two values, it is irrelevant to this discussion since digital electronics deal mainly with binary values.

An operator, on the other hand, is a rule which takes a pair of variables and, based on their values, it returns a new value. For instance, the AND operator takes a pair of variables and returns 0, unless both variables have the value 1, in which case AND returns a 1. Another important operator in Boolean algebra is the OR operator. OR returns 1, unless both inputs variables are 0, in which case it returns a 0. Any operator that relates exactly two variables is known as a binary operator. Now, it is conceivable for Boolean algebra to define operators which take more than two variables as operands. However, these are not necessary and do not make the algebra any more powerful. Moreover, binary operators are simpler to deal with, so we will deal exclusively with binary operators in this discussion. It is possible to define

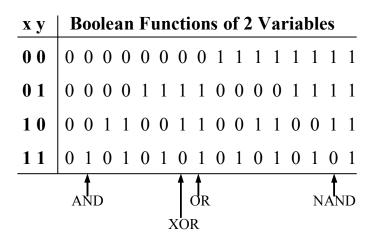

a whole host of possible operators in Boolean algebra. Even if we only consider binary operators, such as we are here, there are 16 possible operators that can be defined (figure 1). However, only certain operators are useful or desirable. Indeed, some are used much more commonly

**Figure 1.** All possible Boolean functions of 2 variables, with some commonly used functions noted.

than others. The two operators mentioned already—the AND operator, along with the OR operator—are the two most commonly used. This is most likely the case because they were in the original conception of Boolean algebra. Additionally, they correspond very nicely with logical operators that human beings use in everyday situations. The exclusive-OR operator, or XOR, is also commonly used and will be featured prominently in discussions that follow. With XOR, a 1 is returned whenever the input variables differ in their values. Otherwise, XOR will return a 0. There are some other functions, such as NAND and NOR, which are commonly used in circuit designs, but will not be used very much in this paper. The reasons for selecting AND, OR and XOR to be our major operators in this discussion will become obvious later. Suffice it to say, however, that this selection of operators is powerful, intuitive and follows in the example of previous research that has been influential in this area.

It should be noted, additionally, that NOT will be used as a separate operator for the discussions in this paper. NOT only takes one input variable (otherwise known as a *unary* operator) which simply returns the complementary value of the input variable. Though simple, this is a very useful operator to include. It will be symbolized in this paper with an apostrophe (as in X', the complement of X). In the truest conception of Boolean algebra, there is no need for an operator of this type because variables are all defined as having complements. The reason we include it as a separate operator is that it makes the transition to talking about real circuits easier. In most cases with circuits, complements are not simply available in the way they are thought of in Boolean algebra. Rather, they must be provided through the use of extra circuitry. Therefore, when we are designing circuits, we want to recognize this fact and make sure that it is explicit, rather than implicit, in the process.

Now, variables and operators are used to build up Boolean functions. A function is an algebraic expression that is constructed by combining some number of variables and operators, along with an equal sign [6]. On the other side of the equal sign from the variables and operators is the function name. The function can take on the value 0 or 1, similar to the variables of which it is composed. Of course, the value of the function depends entirely on the value of each variable and the configuration of the operators within the function. For instance, consider the Boolean following function, named 'F', as a simple example (n.b. 'AND' is symbolized by '.', and 'OR' by '+'):

$$\mathbf{F} = \mathbf{X} \cdot \mathbf{Y} + \mathbf{X} \cdot \mathbf{Z} \quad (1)$$

This function is composed of three variables: X, Y and Z. It also has four operators: two ANDs, one OR and a NOT. It can be determined that this function has a particular behavior. In other words, F is equal to 1 in certain specific instances and it is equal to 0 in others. More specifically, F equals 1 if X = 1 and Y = 1, or if X = 0 and Z = 1. Otherwise, the function equals 0.

Since this function is fairly simple, it is possible to see this behavior by simple examination. However, the most comprehensive approach to determining the behavior of this function is to write its truth table (figure 2). In other words, one can exhaustively list all the logical situations which apply to the function. To construct a truth table, one must first list which variables are present in the function. In the case of our current example function, the variables are X, Y and Z. Then, one must exhaustively list all the possible value combinations that these variables can take on. Each row represents a different combination.

| XYZ | <b>X'</b> | X'*Z | X*Y | X*Y+X'*Z |

|-----|-----------|------|-----|----------|

| 000 | 1         | 0    | 0   | 0        |

| 001 | 1         | 1    | 0   | 1        |

| 010 | 1         | 0    | 0   | 0        |

| 011 | 1         | 1    | 0   | 1        |

| 100 | 0         | 0    | 0   | 0        |

| 101 | 0         | 0    | 0   | 0        |

| 110 | 0         | 0    | 1   | 1        |

| 111 | 0         | 0    | 1   | 1        |

**Figure 2.** The truth table for the 3-variable Boolean function  $F = X^*Y + X^*Z$ .

Next, one must determine the value of the function for each row, given the variable values that are listed there. To do this, it is easiest to simply "plug in" the variable values, apply the operators by hand, and then discover what the value of the function is in each situation. For our example function, F, we see that only certain rows in the truth table list a 1 for F's value. If we look closer, we see that these rows correspond to situations where either X = 1 and Y = 1, or where X = 0 and Z = 1.

Just as it is possible to list the truth table for a given Boolean function, it is also possible to derive a function from a truth table. In fact, doing this is not at all complicated. The simplest method relies, primarily, on a particular type of Boolean function called a minterm. A minterm is equal to 1 in one, and only one, row of the truth table. Furthermore, a minterm can be defined by simply examining the variables which are listed in the single row of the truth table where the minterm equals 1. The minterm function is then defined as an AND-ed group of those variables (also known as a *product*), where the variables in that row with a value of 0 are complemented. Consider, again, the truth table for our example function, F (figure 2). If we wanted to make a minterm that equals 1 in the row where X = 1, Y = 1 and Z = 0, we would define the minterm thusly:

$$m_6 = X \cdot Y \cdot Z'$$

(2)

Note that X and Y are in their true (uncomplemented) form, but Z is complemented. This corresponds to the values of the variables in the specified row. Furthermore, this function,  $m_6$ , is equal to 1 in only the specified row. Also, note that the name of the minterm,  $m_6$ , indicates that the only 1 is located in the 6<sup>th</sup> row of the truth table. This last item is by convention.

If we understand how to construct minterm functions, it is easy to then use the minterms to construct a more complex function. First, a minterm must be constructed for each 1 located in the rightmost column of the truth table. In other words, there must be one

minterm function for each situation in which the function equals 1. Second, a new function must be constructed which simply ORs (or sums) the minterms together.

It is beneficial, of course, to go through a quick example. Going back again to our example function F (figure 2), one can see that there are four rows in which the function equals 1. The following minterm functions can be derived from those four rows, in exactly the same way as before:

$$\mathbf{m}_1 = \mathbf{X} \cdot \mathbf{Y} \cdot \mathbf{Z}; \ \mathbf{M}_3 = \mathbf{X} \cdot \mathbf{Y} \cdot \mathbf{Z}; \ \mathbf{M}_6 = \mathbf{X} \cdot \mathbf{Y} \cdot \mathbf{Z}'; \ \mathbf{M}_7 = \mathbf{X} \cdot \mathbf{Y} \cdot \mathbf{Z}$$

(3)

Once these functions have been constructed, the next step is to combine them. They will be summed together to form a new function. The function is as follows:

$$F = X' \cdot Y' \cdot Z + X' \cdot Y \cdot Z + X \cdot Y \cdot Z' + X \cdot Y \cdot Z \quad (4)$$

This function will show the exact same behavior as described in the truth table for function F (figure 2). Moreover, it will also show the same behavior as the previous function given for F. Indeed, the two functions are equivalent, even though the forms are different. The latter, longer form of F can be thought of as a complete listing of where the function is equal to 1. However, the complete listing is not necessary to specify the target function. Rather, some amount of condensing can take place. The prior form of F represents such a condensed version.

## 2.2 Logical Forms and Simplification Techniques

The different forms of F that are given, above, are examples of two very important forms. The latter, wherein all the minterms are listed in the function, is known as a canonical form. Canonical forms often contain more operators than other formulations, but they also require the least amount of effort to arrive at. Indeed, we have just seen how simple it is to construct a function in canonical form. There are other types of canonical forms, as well, which depend on a complete listing of rows that are equal to 0 (known as maxterms). These canonical forms are equally easy to construct. However, canonical forms almost always require more than the minimum number of operators.

The prior form of F is a type of standard form. Functions in that standard form are still composed of AND terms connected by ORs, but require fewer operators. This form is also called sum-of-products. Other standard forms are composed of OR terms connected by ANDs (product-of-sums), while still requiring fewer operators. One can think of functions in standard forms as being similar to those in canonical form, only they are condensed.

It is usually desirable, as one might expect, to have a function with fewer operators. Hence, standard forms are usually desirable, since they are smaller. Remember that the first form of our example function, F, was a type of standard form. Moreover, this form of F required only 4 operators (2 ANDs, 1 OR and 1 NOT), whereas the canonical form requires 15 (8 ANDs, 3 ORs and 4 NOTs). That is quite a substantial savings in the number of operators. Fortunately, the route to constructing a function in standard form is fairly straightforward. There are several established methods which make it easy for human beings to put functions into standard forms. These methods are commonly known as logic simplification techniques, for obvious reasons.

These methods usually focus on convenient ways to group minterms together into smaller expressions. It is possible that several minterms may be covered by a much smaller term and will not need to be listed, exhaustively, in the function. To borrow an example from our function F once again, we can consider the minterms listed in the canonical form. Remember, all the while, that the terms are OR-ed together in this canonical form of the function. Therefore, if any term is equal to 1, the whole function is equal to 1. Specifically, the first two minterms listed are X'·Y'·Z and X'·Y·Z. Notice that both terms contain X in complement form and Z in true form. The variable Y, on the other hand, is seen variously in true and complement form. Logically, we can take this to mean that if X = 0 and Z = 1, the value of Y doesn't matter. Either way, one of the terms will be true, and consequently the whole function will be true. Therefore, we can say that the entire function will be true if X = 0 and Z = 1, without consideration for Y. So, we replace the first two minterms with, simply, X'·Z. Doing so does not change the behavior of the function at all. The first two minterms of the function are "covered" by the shorter term.

This type of condensing is exactly what the simplification techniques aim to do. Of course, they formulate the idea of condensing in a much more convenient way. With the methods, the choices for which minterms to condense are made more obvious. One method, called the Karnaugh Map method, presents the minterms as an array of 1s and 0s. The goal is to draw the largest boxes possible around groups of 1s or 0s. Once this is done, the term which replaces them is simply a grouping of their common variables [6]. Another method,

called Quine-McClusky for its creators, avoids the map representation in favor of an ordered listing of the differences between minterms.

Sometimes these methods are called minimization techniques, implying that they generate functions which use the fewest number of operators. However, this is a bit of a misnomer. There is no guarantee that a function constructed through these methods is in its smallest form. The trouble, however, is not with the methods, but with the form itself. Indeed, there is no guarantee that the standard form of any function is the smallest possible form. Despite this, standard forms are extremely important for two main reasons. First, they are easily obtained by certain methods, for example, those mentioned above. Second, they are smaller than the canonical form. In some instances, they are substantially smaller, as was the case with our example function, F. One problem, however, is that standard forms are just that, standard. By definition, they always have the same basic properties. The functions that result from using the methods above are either in sum-of-products or product-of-sums form. However, we know from our earlier discussion that many, many possible combinations exist, and many of them are not in standard form. Although this standardization makes the functions easy to produce, at the same time, it sometimes makes them limited in terms of minimization. Although it is possible for a function in standard form to utilize the absolute minimum number of operators, in many instances this is not the case. If one is open to arranging operators in very unconventional ways, there may be other functions which behave identically while making use of even fewer operators.

Now, the reason why all information about this Boolean functions is relevant here, is that the digital logic of computers is simply an implementation of the ideas from Boolean logic. Indeed, the variables of Boolean functions are simply the same as inputs to logic circuits. Similarly, the logical operators

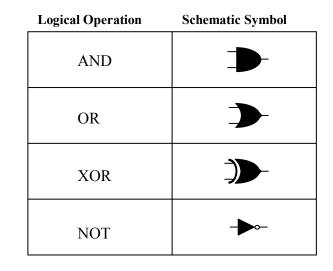

**Figure 3.** The names of logical operators that are important to this work paired with their schematic symbols.

in Boolean functions are implemented with logic gates in circuitry. Refer to figure 3 for an illustration of logical operators and their corresponding logic gate schematic symbols. Just as in Boolean algebra, where variables and operator are combined in endless ways to create new functions, so are inputs and gates combined and connected in different ways to create new circuits. The output of a logic circuit is determined by the behavior of the function it implements.

Hence, the discussions of logic simplification methods, and the limitations thereof, also applies to the design of logic circuits. Rather, the ability of simplification methods to cut the number of logical operations is even more crucial when we talk about implementing circuits. The reason is simple, every logical operation is another piece of physical circuitry that is necessary to include. In order to not waste materials, and to make our circuits more efficient, we must ensure that our circuits are as small as possible.

The difficulty of exploring a larger diversity of functional configurations, however, is that the number of configurations quickly balloons. As we relax the limitations on the types of configurations we will consider, the numbers begin to mount. Furthermore, if we then try to consider circuits with more inputs and a broader variety of gates, the numbers climb even faster. It soon becomes impossible to think of a human being doing the designing. There are simply too many combinations to consider. Hence, it is desirable to employ computers for the task of circuit design. Surely, they can analyze possible solutions many times faster than human beings can. In doing so, they may be able to find circuit designs which are more efficient than any design a human could devise; at least, more efficient than a human could devise in a reasonable span of time.

As we begin to talk about automating the design process, our main concerns change. No longer are we worried about analyzing the logic behind the circuits, or about coming up with good designs on our own. These concerns should be passed on to the computer for consideration. Mainly, we should be concerned with properly formulating the problem so that it can be automated. Also, we should be concerned with finding the correct automation process. That is, a process that produces agreeable results, and that is reasonably efficient. An exploration of these new concerns has already begun in the literature. Surprisingly, perhaps, many of the concerns are being put to rest by using ideas from artificial intelligence.

## **3** Search Techniques from Artificial Intelligence

Artificial intelligence techniques have been crucial in automating logic circuit design. Specifically, the idea of search algorithms has led to some important gains in this type of automation. Before it is possible to fully appreciate the reasons for this, however, it is important to review the essential aspects of artificial intelligence search techniques. The discussion presented here, similar to that given in Section 2, is not intended to be comprehensive. Rather, it is a review of major concepts and certain specific details, given with an eye towards automating logic circuit design. The research which will be presented in this paper follows two distinct approaches. These two approaches are distinguished by the search techniques from which they are built. Namely, they are based on types of systematic search and local search. As such, the following review of search concepts will begin with systematic search, and proceed to local search. Afterwards, a clearer connection to logic circuit design can be made.

#### 3.1 Search Basics

Solving problems by searching is a powerful and useful idea. It is a way to get to a solution by examining different sequences of actions, when there is no single action which solves the problem [28]. Many problems can be formulated in a way which agrees with the search paradigm. To do so, one must first formulate a representation for the state of the problem as it currently is. This is known as the initial state. There must also be the concept of a goal state, what the problem looks like when it is solved. Next, one must determine a

series of legal actions which are to be carried out on the initial state. By performing the legal actions, it is possible to create successors of the initial state. Legal actions may then be performed, in turn, on the successor states. Hopefully, some actions will lead towards the goal. Thus, one must have a test which determines if any state represents the desired goal. This is known as the goal test. At each step, when a state is selected to have an action performed on it, the goal test is applied to make sure it isn't already a goal state. If it is, then the sequence of actions that was used to get from the initial state to the goal state represents a solution to the problem.

Often, there are multiple ways of getting from the initial state to a goal. In these cases, one solution can be preferable over another. It is possible to determine quality of solutions by considering the number of actions required to get from the initial state to the goal. Additionally, different actions may have different costs associated with them. If this is the case, then the costs can be summed, rather than just considering the number of actions.

The name "search" refers to this technique because it is applying many combinations of actions to the initial state, in *search* of an acceptable combination. An acceptable combination is one which constitutes a solution, and which is low enough in cost to satisfy some specified criteria. Once an acceptable combination is discovered, one can get to the goal state by applying the sequence of actions that are specified in the solution.

For an example of problem-solving via search, consider the classic route-finding problem [28]. Specifically, assume we are in New York City, and we want to travel by car to San Francisco. That is, our initial state is us being located in New York. Our goal is to be located in San Francisco. Our goal test, for lack of a global positioning system, will be to scan the horizon for the Golden Gate Bridge. The problem, obviously, is finding a good route to travel. Which cities should we travel through on the way to our destination on the west coast? At each step, the legal actions are to drive to any of the nearby cities on a highway. We may chose to drive south first, to Philadelphia and then on to Washington. On the other hand, we could go west to Buffalo and then continue to Detroit. There are many possible paths to choose from, any one of which may constitute an acceptable solution. Note, too, the distinction between the goal and the solution. The goal is to be in San Francisco. The solution, on the other hand, is an acceptable path to get from here to there. Once we have a solution (i.e. a path), we can apply the actions that make up the solution to achieve our goal (i.e. to get where we are going).

Before continuing, there is some terminology which must be explained. Search is often thought of as building a tree structure which is called a *search tree*. For instance, the tree which is formed by recording all highway paths as one leaves New York is a search tree. The nodes of the tree are called *search nodes*. Each node in the tree corresponds to some state of the problem, such as being in New York. The root of the search tree is the initial state, and when the successors of that node are generated through the application of legal actions, the search tree begins to grow. Generating all of the successors of a node, through the application of all legal actions, is known as *expanding* that node. In practice, the successors of a node are always generated all at once, rather than at separate times. Therefore, expanding is an important concept. Now, any node which is in the tree, but has not been expanded, is known as a *fringe node*. The set of all fringe nodes is, intuitively, known as the *fringe* of the tree. At the beginning of any search, the fringe is composed entirely of the initial state. The first step is always to expand the initial state, and then all of

its successors become the fringe. Once it has been expanded, the initial state, or any other expanded node, is no longer a part of the fringe.

The route-finding problem offers us a fine example to explain this terminology. The root of the search tree is the initial state, namely the state of being in New York. Expanding the root node creates several new nodes, all of which branch out from the root. In expanding, we apply all legal operators for driving out of New York. Legal operators in this case may be driving South, North and West. Note that driving east may be a sensible operator for the problem as a whole, but it is not a legal operator for the case of driving from New York (unless your car is amphibious!). The new nodes which are generated might represent the state of being in cities near to New York, such as Philadelphia, Buffalo, etc. These new nodes also compose the fringe of the search tree, because they have not been expanded themselves. As we expand nodes, the paths we are searching become longer and longer. Hopefully, we will eventually reach our goal of being in San Francisco.

#### 3.2 Systematic Search

Different search algorithms are distinguished by the order in which they choose to expand the fringe nodes [28]. By choosing different orders of expansion, some may find answers more quickly, and some may find answers that are superior. The search paradigm is very broad, and there are many variations on the fundamental ideas. Some of the oldest and most widely used variations fall under a broad sub-category which can be called systematic search. Search techniques in this category are systematic, not because they leave no stones unturned, so to speak. Although, that is certainly an option. Rather, they are systematic because they keep track of which search options have been explored and which haven't [28]. This is done by keeping the entire search tree in memory as it develops. In this way, they can ensure that all search options which are deemed relevant can be explored. There are alternatives to systematic search, and they will be seen later.

Systematic search is, perhaps, best exemplified by its simplest and most intuitive manifestation. Specifically, the type of search known as breadth-first search (BFS). It illustrates the ideas of systematic search very nicely, including all of its strengths and weaknesses. BFS explores all possible options at each step, until a solution is found. What this means, in practice, is that the initial state is expanded, followed by all the successors of the initial state, then all the successors of those successors, and so on until a solution is found. In other words, each level of the tree is explored completely before heading further down the tree.

Not only is BFS systematic, but it is exhaustive. It considers all possible search paths at each step. Therefore, it will always find a solution if one exists. This is a very desirable property. Moreover, by considering nodes closer to the root first, BFS will always find the solution which is shallowest in the tree. In most cases, this shallow node will also represent an optimal solution. In fact, if the problem is properly formulated, one can be guaranteed that BFS will find the optimal solution. Again, this is a highly desirable quality for a search algorithm to have. The downside of BFS is that for many problems, its time and memory requirements are highly impractical. Not only does each fringe node need to be considered at each step, but each node and its successors all need to be kept in memory as the search carries on. As a result, both time and memory requirements grow exponentially with the depth of the tree.

There are ways to cut down the costs associated with an exhaustive search method such as BFS. One such way is with the use of heuristics. A heuristic is a problem-specific function which serves an important purpose, it estimates the cost of getting from any node to the goal node. With the information provided by heuristics, a search algorithm can determine which nodes may be closer to the goal, and thus make more informed decisions about the best node to expand next. By choosing more wisely from the fringe, an algorithm can potentially avoid expanding many nodes which lead down undesirable paths. It is important to emphasize that heuristics can only estimate, though. If one could always know the exact distance, then the problem would essentially be solved and searching would be completely trivial.

For our route-finding problem from New York to San Francisco, a good heuristic might be to take the straight-line distance from each location to San Francisco. This distance stands as an estimate of the highway distance which we would travel on the actual drive. However, the estimate is probably pretty accurate, to within a certain degree. If we actually knew the highway distance from any location to San Francisco, the problem of finding a good route would be trivial. Thus, an estimate will suffice.

Some heuristics can produce estimates which are highly accurate. If an accurate heuristic is used, then the algorithm is more likely to expand nodes that are relevant to good solutions. Nodes which lead to bad solutions, or no solutions, can be avoided altogether. The savings in time and space for search algorithms can be substantial. Moreover, if heuristics are used carefully, one can still be guaranteed that the solutions will be optimal.

The most immediate problem with heuristics, however, is that they can be quite difficult to design. They require specialized, in-depth knowledge of the problem at hand.

This can take time and a great deal of effort. For some problems, it may be nearly impossible to accurately estimate the cost to the goal. There is a more general problem, as well. Even with excellent heuristics, systematic search methods can still utilize large quantities of space in memory and take a long time. To some extent, this is the price to be paid for the benefits and guarantees of a search which is systematic.

#### 3.3 Local Search

There are alternatives to systematic search. Some search algorithms take a completely different approach to the concept of search. Indeed, they are intended to work on a completely different formulation of problems. For formulation of some problems, the path to the goal doesn't matter. All that matters is being at the goal. In these situations, it is not necessary to keep track of the path from the initial state to the goal state. Rather, it is sufficient to keep track of only a single state. This state, known as the current state, represents the situation as it currently stands. At each step, we can apply some operators to the current state to alter it, just as before. The main difference here, though, is that once the operator has been applied to the current state, the new state replaces the old state. There is no keeping track of the global picture, where the search has been or what decisions were made. Hence, this type of search is known as local—as opposed to systematic, or global—search.

To clarify local search, we will follow an example, fairly closely, from Pfeifer and Scheier's book *Understanding Intelligence* [26]. Suppose we are given a string of 10 letters that is completely random. For the sake of explanation, say the randomly generated sequence of letters is "wlmldtjbkp". The goal is to make this string spell the target word "university". However, we don't know the target string. Instead, all we have is an evaluation function which, when presented with a string, can tell us how many correct letters are in their correct positions. So, we begin searching in a simple fashion. At each step, we produce five copy strings, and randomly change one letter in each. Each string is then fed into the evaluation function and rated based on the letters it shares with the target. The more letters it shares with the target, the better. The best string of the five then replaces the initial string, and the other four copy strings are erased. Eventually, by selecting the best string at each step, we will arrive at a string that matches completely. Note that there is no record of the search procedures that takes place. During each step, the memory requirements never exceed that of 60 letters. The requirements will never grow, either, as the algorithm proceeds. Also note that, even if we kept the records around, they would be virtually useless once an answer was found. We don't care how we got to a matching string, in this case. All we care about is that we did match the target string. This type of local search algorithm is known as hill-climbing because it always moves in the direction of increasing or equal value [28]. It is, perhaps, the simplest local search algorithm, but it is also quite effective.

Local search algorithms vary in how quickly they can converge on solutions. Many different algorithms exist, and each is different. However, even simple algorithms, like the one presented above, can find solutions after only a small number of steps. Small, that is, relative to the 26<sup>10</sup> possible letter arrangements in a 10-letter string. Also, local search algorithms offer huge savings on space requirements, especially as compared to systematic search algorithms. The space requirements are usually constant throughout the algorithm's runtime.

On the other hand, erasing the records of a search has its detriments. Some common local search algorithms cannot even guarantee that they will find solutions. This is because, without records of past search activities, it is impossible for an algorithm to reconsider old options. Without this ability, the algorithm cannot tell if it is stuck in a local maximum, or some such sticking point in the search space [28]. In essence, this is the downside of removing the systematic element of searching. Although, local search often does find solutions. There are many ways to alter the simple algorithms so that they are much less prone to getting stuck. A related problem is that these algorithms often cannot guarantee any level of quality in solutions. The algorithm might find one solution, but could get stuck and never discover that there is an even better one. Despite these problems, there continues to be much attention on local search algorithms because of their benefits.

One type of local search algorithm which has attracted much interest is genetic algorithms (GAs). These algorithms attempt to capture the power of one of biology's most powerful concepts: natural selection [14]. GAs were first proposed in 1975 by John Holland, in his work entitled *Adaptation in Artificial and Natural Systems* [9]. Like our hill-climbing example, GAs have space requirements that are small and have a fixed ceiling. However, GAs are not so drastic in cutting the amount of nodes they keep around. Rather than one current node, there can be many, perhaps even hundreds. The number is finite, though, and usually still small with respect to the entire search space. In GA terminology, this finite set of nodes is known as a *population*. Each member of the population is known as an *individual*. As above, an individual is commonly represented as a string of numbers or characters. Even if the problem doesn't involve strings in the solution at all, the different problem states are still converted into string representations. This is meant to be similar to

the method of encoding in DNA, and how protein sequences are encoded with a four-letter alphabet. At each step, an entirely new set of individuals will be constructed from the individuals in the current set. All the individuals in a set at one time are, together, called a *generation*. It is the method of producing a new generation that makes GAs so unique. The method attempts to simulate sexual reproduction.

Going back to our string-generation example from above, let us formulate the problem for a GA. Instead of one random string at the beginning, we start with some finite number larger than one. Say it is 50. To begin the construction of a new generation, the GA first evaluates each of the 50 strings by submitting them, as before, to the evaluation function. In the case of GAs, the evaluation function is known as the *fitness* function, since it fits with the biological terminology. The more fit an individual is, the better. For the string-generation problem, the fittest possible individual would be the string "university".

Once the fitness scores are obtained for all 50 strings, pairs are chosen from the among the 50 for reproduction. Each pair will yield a new pair of strings via reproduction, so we choose 25 pairs to keep the population size the same. The pairs are chosen randomly, but are weighted with respect to the fitness scores. Thus, the pairs are largely composed of individuals with higher fitness scores. Some extremely fit individuals may be chosen several times for pairing. Also, lower-scoring individuals always have some chance of being chosen. The reality, though, is that extremely low-scoring individuals may never be selected at all for any pair. Again, all this is intended to simulate the biological situation in which the more fit organisms pair off for reproduction.

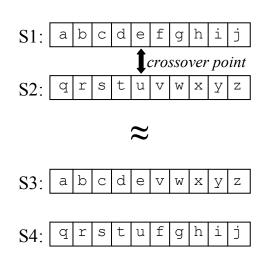

During the reproduction phase, each pair is subject to *crossover* (figure 4). During crossover, a point is chosen at the same position in both strings in a pair. Both strings are

then spliced at that position and the pieces after that point are exchanged between strings. For instance, if the crossover point is at the  $3^{rd}$  position in the pair, then the  $4^{th}$  through the  $10^{th}$  letters of the first string will be exchanged with the  $4^{th}$  through the  $10^{th}$  letters of the second string. Finally, each position in each of the strings has an independent probability of being mutated. That is, the letter will be randomly changed into a new letter. The mutation probability is predetermined and is usually fairly small. One additional operation that can take place during reproduction is *elitism*. This means that the best string from one generation will always be carried over, unchanged, into the next generation. Though this idea is questionably biological, it is a practical consideration. It prevents the best idea yet from simply vanishing in the coming generation. This, despite the fact that searching is still proceeding.

Crossover is the operation that makes GAs truly unique. Combining crossover with

**Figure 4.** During crossover, strings (S1 and S2) are spliced and recombined to create new strings (S3 and S4) around the crossover point.

the more basic idea of random mutation is also unique, and powerful. Mutation also allows for exploration of random parts of the search space [28], while crossover allows trading and exchanging of ideas from different strings. This combination seems to be extremely effective in finding solutions. Indeed, they have

had substantial impacts on many types of problems. Aside from their effectiveness, they also share many of the general benefits of local search, most notably the reduced space requirements. However, there is still a lot that is unknown about how effectively GAs operate in general and why it is that GAs seem to work so well. They also suffer from the problems of the local search paradigm. Specifically, they are not systematic or exhaustive, and they make very few guarantees about the quality of solutions they can produce. Nonetheless, they continue to capture the interest of many researchers for their ability to successfully negotiate a wide variety of problems.

# 4 Applying Search Techniques to Logic Circuit Design

Automating logic circuit design is both desirable and difficult. The design process can involve sifting through an immense number of gate configurations to find the optimal one. Fortunately, search techniques were designed for sifting through immense numbers of configurations. It is an obvious progression to consider search for finding combinations of logic gates. Search has been used to successfully solve such diverse problems as robot navigation [30,31,32,33], puzzle solving [28] and DNA strand alignment [5]. It has been used to find desirable and winning combinations on chess boards. With the proper formulation, the problem of designing logic circuits does not look dissimilar to any of the problems for which search is normally used.

Formulating the problem for search is fairly intuitive. Gates and the connections between them are taken as the primitive search elements. In other words, the search proceeds by combining and rearranging gates and connections. There is some selection of gates which is predetermined and available for inclusion in the circuit. Each type of gate can be used in the design, or not. For the sake of simplicity, only two-inputs gates are usually considered. Each individual gate gets its inputs from either the circuit inputs or from other gates. The outputs from each gate can either connect to the inputs of another gate, or they can contribute to the overall output of the circuit. Usually the circuit's overall output comes from some single, designated gate. The overall number of used gates can grow or shrink during the search.

The primary goal for this type of search is, obviously, to produce circuits which are fully functional. That is, the circuits must produce the correct outputs for each of the possible inputs. The functionality of a certain configuration might be tested by building a physical circuit and testing it. Alternatively, one can choose to simulate the circuit's operation. Such a simulation entails propagating the logical values of the inputs through the circuit. Beginning with the inputs, the values proceed through the gates layer by layer, just as they would in a physical circuit. At each gate, the appropriate logical function is applied. When all the values have been propagated, the value of the designated output gate is read. This must be done for every possible combination of the input values. If all the output values match their respective input combinations, then the circuit is fully functional. Functionality is not the only concern, but it is always the most important concern. Other secondary criteria may be part of the search as well, such as size, depth, power dissipation and gate selection. Information about these criteria are easily obtained by examining the circuit. For instance, the size of the circuit can be determined by simply counting the number of gates which are used.

## 4.1 Genetic Algorithms for Logic Circuit Design

Up to the present, most research has focused on using local search algorithms for the design of logic circuits. More specifically, genetic algorithms have been the most common choice. One reason why local search has been preferred is that the search space for logic design is enormous. Indeed, we will see later that search space grows exponentially with the number of gates required. It is so large that space-saving nature of local search seems to be a necessity. Another reason why local search has been preferred is that only the end-product of the search seems to matter. As we saw before, local search does not remember the path from the initial state to the goal state. Therefore, it is suited for problems in which the path to the goal state is irrelevant. In other words, the goal state must constitute a solution all by itself. It seems intuitive that logic circuit design fits this mould. It should not matter how the search progresses, as long as the good circuit is produced in the end. Therefore, it seems pointless to use a systematic search technique which remembers the entire search path. Not only is the space required for that information huge, but it is not useful anyways. We will see later that the path information becomes relevant if the problem is re-formulated. However, with the more obvious formulation, local search seems to be best choice.

GAs are the most common search algorithms used for automating logic circuit design. The research to date has favored their use overwhelmingly. Often, this has lead to great success as GAs seem well-suited for this purpose. In order to use GAs for this purpose, though, there must be some additional formulation of the problem. As we have seen, GAs use strings as their basic elements, in the same way that biological systems use DNA strands. Therefore, if we are to use GAs for circuit design, all of the information about gates and connections must be encoded in a string. In accordance with the terminology from biology, this string is known as the "genotype". The genotype is an encoding of all the relevant information about the circuit. The relevant information which is encoded is known as the "phenotype". The phenotype includes the gates used in the circuit, the connections between gates and other essential properties. The phenotype can be derived from the genotype, and in turn, the operation of the circuit can be derived from the phenotype. The way in which the genotype encodes the phenotype varies, since there is no standard method for formulating the encoding. There must be an encoding, however, since it is essential to the concept of GAs. The specific encoding used in this paper will be seen later.

## 4.2 Two GA Camps

From the early investigations, the application of GAs to circuit design has been divided into two camps. These two camps differ, mainly, in the way they implement and test the potential circuits. During the search process, every circuit which is a potential goal circuit must be tested for functionality. This can be done by either physically implementing the circuit and testing it, or it can be done by simulating the circuit's operation [18]. Therein lies the division in this research area. If the GA tests the circuits by first implementing them in hardware, it is said to be performing *intrinsic* evolution. GAs which simulate their potential circuits are said to perform *extrinsic* evolution. Both methods have inherent advantages and disadvantages. It can be difficult to figure out whether hardware or simulation is superior. Indeed, this issue has arisen in other fields of research, and it has

proven equally difficult to resolve. Most notably, there is much debate in the literature of experimental robotics over simulation versus hardware embodiment [37].

The debate over this issue revolves around the long-fought trade-off between getting solutions of better quality and getting solutions more quickly. On the one hand, simulation allows for rapid implementation of circuits. The parameters of the circuits, and of the problem in general can be changed with ease and expediency. The components being utilized can be changed, altered, or even invented without much difficulty. Also, analysis of the circuits is easier since simulations track all of the properties of the circuits by their very nature. For the researcher, this ultimately means more design freedom, as compared to the intrinsic approach [18]. However, the extrinsic approach does limit the overall realm of possible outcomes. By using simulations to evaluate circuit designs, the researcher is necessarily making some simplifying assumptions about the testing environment. In the process, this is essentially circumscribing exactly which circuits will work. It eliminates the possibility that something unexpected might happen, that there is some subtle effect in the design which causes a seemingly useless circuit to function properly [18]. As a result, it is possible that extrinsic evolution will miss some extremely novel design. However, it is possible that intrinsic evolution will produce such novel designs.

## 4.3 Intrinsic Evolution

Implementing the circuits in hardware may seem prohibitively laborious and timeconsuming, unless one recognized the benefits of using Field Programmable Gate Arrays (FPGAs). An FPGA is essentially an array of unassigned logic blocks, with unassigned connections between them [29]. The logic blocks can be programmed to function as logic gates. The connections may be programmed to take on different configurations. What this means is that an FPGA can be configured to function like any number of digital logic circuits. Moreover, this can be accomplished with great speed. Therefore, it is feasible that the circuits considered by a GA can be implemented in FPGAs and tested as real, physical circuits.

The research into intrinsic evolution was thought to have distinct advantages from the early stages. The early work by Thompson [30,31,32,33] attempted to evolve functional circuits intrinsically on an FPGA. The efforts were successful and also showed that extremely novel designs were indeed possible through this approach. Circuit configurations were developed which were quite distinct from human designs. Most notably, it was possible to evolve designs which were characterized by a distinct lack of temporal coordination, the possibility for which would not have existed with a standard simulation [7,30,31,32,33]. Unfortunately, the final designs suffered from several problems. As expected for intrinsic evolution, the analysis of circuit operation proved rather difficult. Unexpected problems also arose from this method. For instance, the novel designs often relied on particular idiosyncrasies of the particular FPGA being used. Therefore, the designs were often not functional when transferred to other FPGAs. Additionally, the designs usually operated, to some extent, in the analog domain. Even though they evolved on the logic blocks of an FPGA, they were not fully digital. This last item is not inherently problematic, but it does make the designs extremely sensitive to voltage and temperature [19], which is another reason why circuits designed in this way are extremely difficult to reproduce.

Work by other researchers attempted to apply this technique to a variety of circuits [7,21,30,31,32,33,34]. By and large, they suffered from similar problems; they were difficult to analyze or were not reproducible. Attempts were made to overcome the latter problem [3,19]. This mainly involved the recognition and purposeful elimination of designs which relied on highly asynchronous signals, analog operation or on idiosyncratic properties of individual FPGAs. Consequently, this also removed all methods for producing novel designs other than strict reconfigurations of components. While this could still produce designs beyond what human designers could do, it restricted intrinsic evolution to the point where it could not produce designs that were any more novel than those produced by extrinsic evolution. In other words, it eliminated the main advantage of intrinsic evolution over the extrinsic version.

## 4.4 Extrinsic Evolution

As a consequence of the troubles with intrinsic evolution, the extrinsic camp has been favored in recent years. However, the research on this did not begun only recently. Rather, it began even earlier than research on the intrinsic methods. Some of the earliest work of was that of Koza [1,14,15,16], which was both foundational and influential. His work focused mainly on analog circuit design, but also touched on using GAs to develop Boolean expressions and logic circuits. The work of Lang [17] further developed the application of GAs to logic circuits. The focus for this early research was on evolving circuits which were functional, but not necessarily optimal according to any other criteria.

An important question from the beginning was how to formulate a logic circuit in a suitable way for the search process. That is to say, what should the phenotype of the circuit look like? This decision determines much about the range of possible circuits and about the computational requirements of the search. For Koza and Lang [1,14,15,16,17], circuits were formulated as trees of gates, which was powerful in terms of the types of circuits it allowed. It essentially allowed any combination of any size to be represented. However, with that power came large demands for memory and computation time. The tree formulation was also shown to produce circuits which were highly redundant [4].

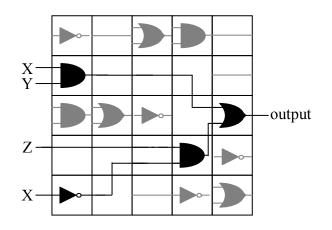

Attempts were made to explore other circuit formulations [11], but the one which has gained the most favor is the array formulation. In this formulation, a circuit is conceptualized as an array of logic gates and connections between them (figure 5). This is conceptually similar to the way an FPGA is structured. At one end of the array are presented the inputs to the circuit, and at

the other end of the array are the outputs. Each gate at a particular location is a member of an array column, and it can get its inputs from any gates in the previous column. The gates in the left-most column get their inputs from any of the circuit inputs, rather than any gates. This formulation was

**Figure 5.** One example of the "array formulation" for logic circuits, which is utilized by the genetic algorithm in this paper as a search node.

developed first by Miller [22,23]. It serves the important purpose of preserving much of the power of Koza's tree formulation [1,14,15,16], in that a large number of configurations are possible. But by loosely limiting the size and the possible connection schemes, it cuts back on the resources needed to support that formulation [4].

Miller [22,23] also intended this formulation to have another important benefit. He used it to optimize his evolved circuits for size. Circuits would begin by evolving in an array of some size. If they could be successfully evolved, then evolutionary process would be repeated again with a smaller array. This would repeat until a circuit could no longer be evolved in reasonable time due to the array being too small. The circuit which evolved in the smallest possible array was considered to be the optimal one [22,23].

The array formulation was influential in the work of many researchers who followed, including the work in this paper. Kalganova [13] altered the array formulation to allow larger circuits to be evolved. This was done by allowing the array positions to take on the functionality of small circuits, as well as individual gates. Larger circuits could be evolved this way, but it is unclear whether these designs were better than conventional designs. Later, Vassilev [35,36] used GAs and the array formulation to optimize circuits automatically. He represented conventional, already functional designs in the array and evolved them towards optimality with respect to the number of used gates.

An important step was taken when Coello [4] put together previous ideas from circuit evolution research and created an algorithm that seamlessly and efficiently automated the evolution of both functionality and optimality. This algorithm also used the array formulation. More importantly, it conceptualized the evolution of functionality and optimality as back-to-back stages. First, circuits would be brought up to fully functional status and then they would be judged on the basis of their other properties. This allowed the evolution of functionality to take precedence, while not dominating any other criteria. This research of Coello [4] serves as the primary basis for much of the research in this paper. That research is the starting point for our attempts to optimize GAs for logic circuit design. As such, there will be more detailed discussion of the work later on, in direct connection with this research.

The benefits of applying GAs to logic circuit design have been as good as expected. By automating the entire process, GAs have been able to quickly develop circuits which are fully functional. Moreover, some circuits which have been developed are superior to those designed by humans [4]. Of course, there is no guarantee that this type of algorithm will return a solution which is better than human designs. Nor is there any guarantee that GAs will return the optimal answer to a design problem. Most of the time, GAs can be trusted to return very good solutions to a logic circuit design problem. However, in order to get guarantees about solution quality, one must turn to systematic search.

## 4.5 Systematic Search for Logic Circuit Design

Depending on the exact algorithm chosen, it is possible for systematic search algorithms to return optimal solutions every time. As we have seen how BFS can exhaustively examine all possible combinations in order to find the optimal solution. In terms of logic circuit design, a search like this would have to examine every possible combination of gates, from one gate up to some large number, until a functional circuit is discovered. If the search proceeded from the smallest number of gates to the largest, the first functional circuit encountered would be guaranteed to be the optimal one with respect to size. However, there is no literature on applying systematic search techniques to this problem. This, despite the fact that solution-quality guarantees are a good thing, and the process seems simple.

There are reasons, though, why some may have thought that looking into this was a bad idea. It is unclear, though, whether those reasons are valid. One reason is that we know search algorithms like BFS can have prohibitively large requirements for memory space and computation time. Since logic circuit design is a problem with a huge number of possible combinations to examine, one might reason that the requirements of the algorithm would quickly make it unfeasible to use. Another reason why systematic search has never been investigated for logic circuit design is that the problem formulation is rather odd. In the intuitive formulation of logic circuit design for search, it would appear that the end-product of the search (i.e. a functional circuit) is all that matters. As such, local search seems to be the obvious choice for solving this problem. However, the intuitive formulation of the problem is not the only possible one. Logic circuit design can be formulated for systematic search, even if it seems strange. By doing this, it will be possible to see whether systematic search is actually as impractical for this purpose as it may seem. If it is not so impractical, we will also be able to see what optimal solutions look like for various circuits of our choosing. In any event, we will be seeing it for the first time.

## 5 Optimization of Genetic Algorithms